研讨会精华分享四:成功率和可靠性驱动的纳米尺度集成电路设计方法学

11月16日,由深圳市有限元科技有限公司&达索系统Simulia联合主办的“第二届电子产品性能设计提升研讨会”,在深圳深航酒店成功召开。此次“电子产品性能设计提升”主题研讨会,旨在通过会议搭建一个开放的技术交流平台,分享电子产品设计方面的成果与经验,共同探讨电子领域面临的技术难题。以下,将为大家分享会议精华四:成功率和可靠性驱动的纳米尺度集成电路设计方法学(教育部长江学者曾璇博士报告)。

研究背景

集成电路是二十世纪五、六十年代发展起来的一种新型半导体器件。它是经过氧化、光刻、扩散、外延、蒸铝等半导体制造工艺,把构成具有一定功能的电路所需的晶体管、电阻、电容等元件及它们之间的连接导线全部集成在一小块硅片上,然后焊接封装在一个管壳内的电子器件。六十年来,以单晶硅为主的半导体集成电路,已经变得无处不在,成为整个信息技术的强大支柱。依赖于集成电路存在的计算机,手机和其他数字电器成为现代社会结构不可缺少的一部分。集成电路带来的数字革命是人类历史中最重要的事件。

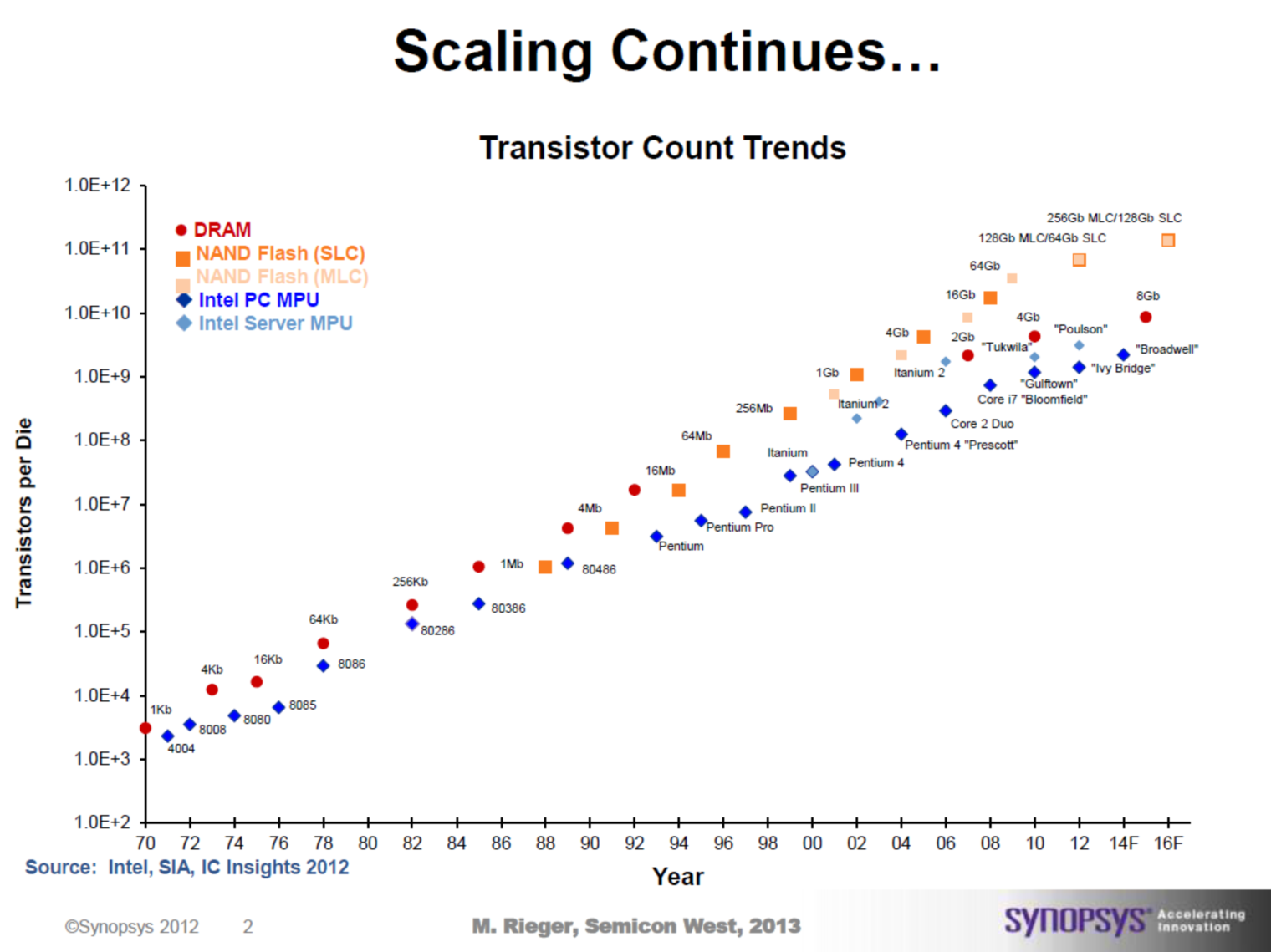

集成电路的制造以及设计技术的不断突破也使其本身有了飞速的发展。早在1965年Gordon Moore (英特尔创始人之一)就曾预言:当价格不变时,集成电路上可容纳的晶体管数量大约每隔18个月便会翻一番,性能也将提升一倍。回顾从那时到现在这个领域的发展情况,确实如他所说。为提高性能,人们不断地按照这个规律提高单个芯片上硅晶体管的数量。

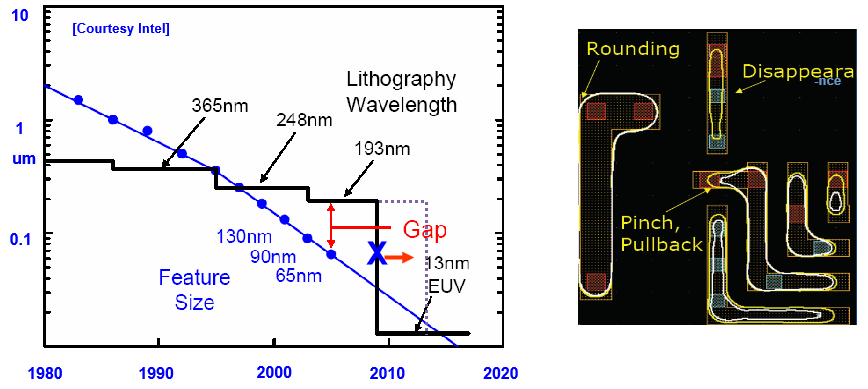

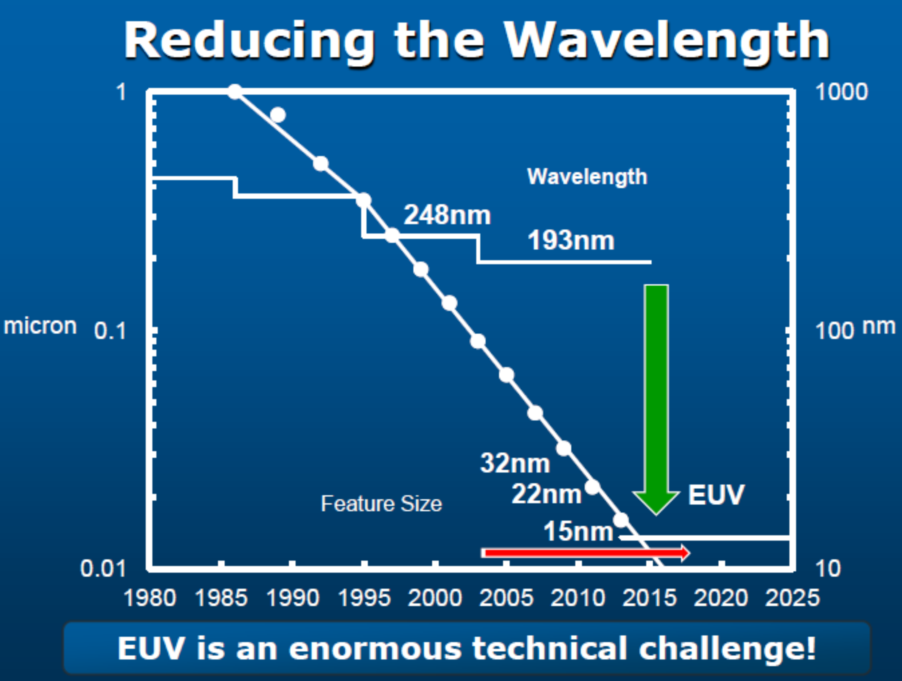

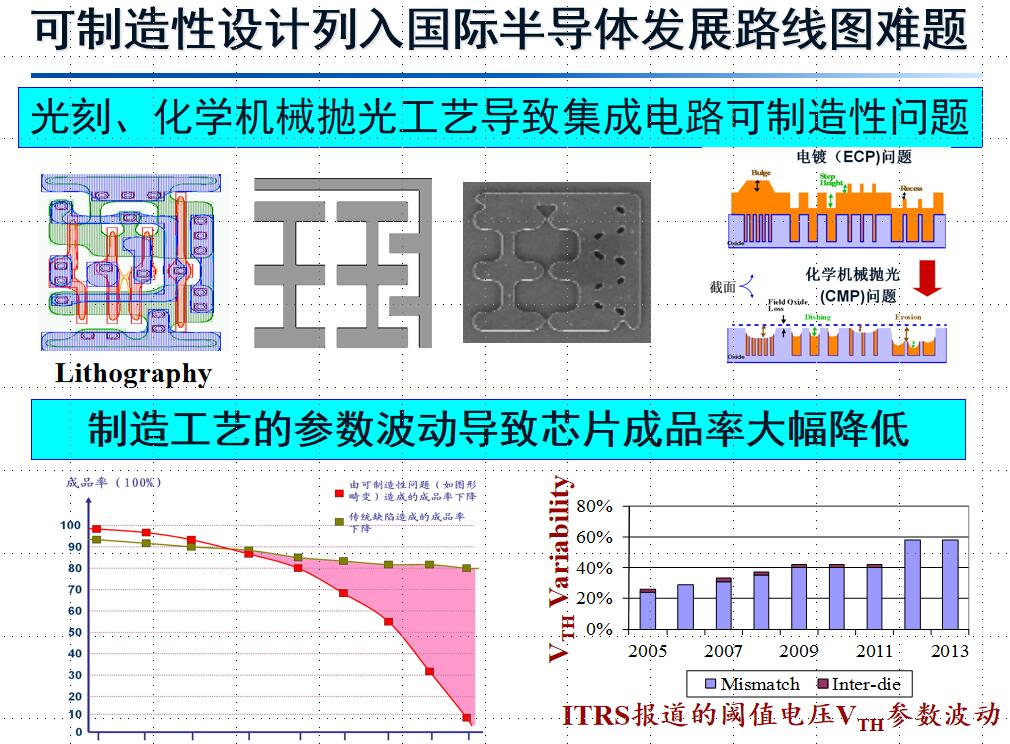

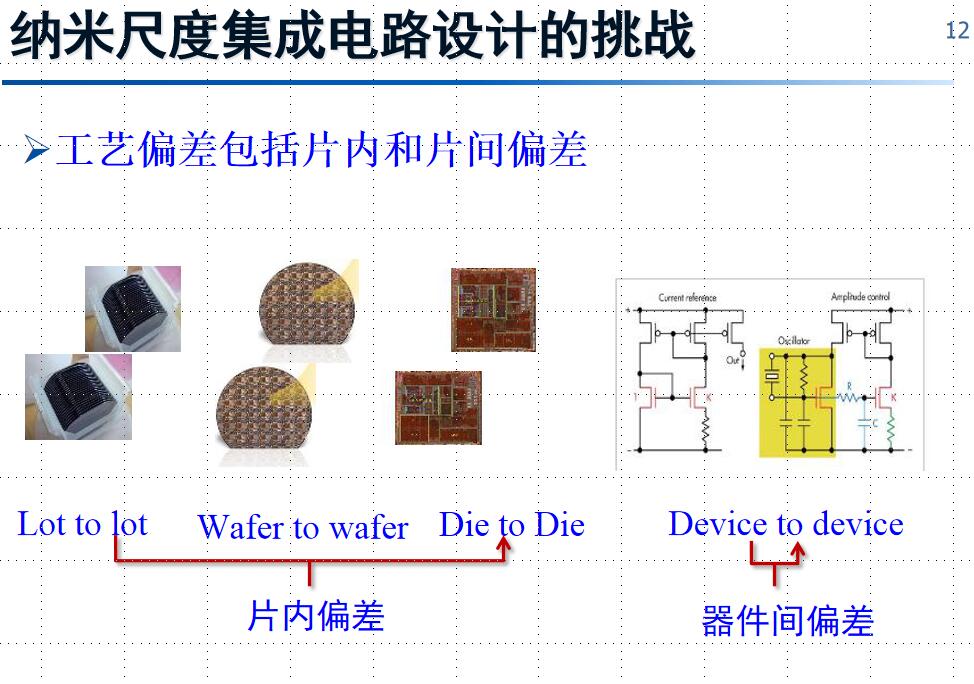

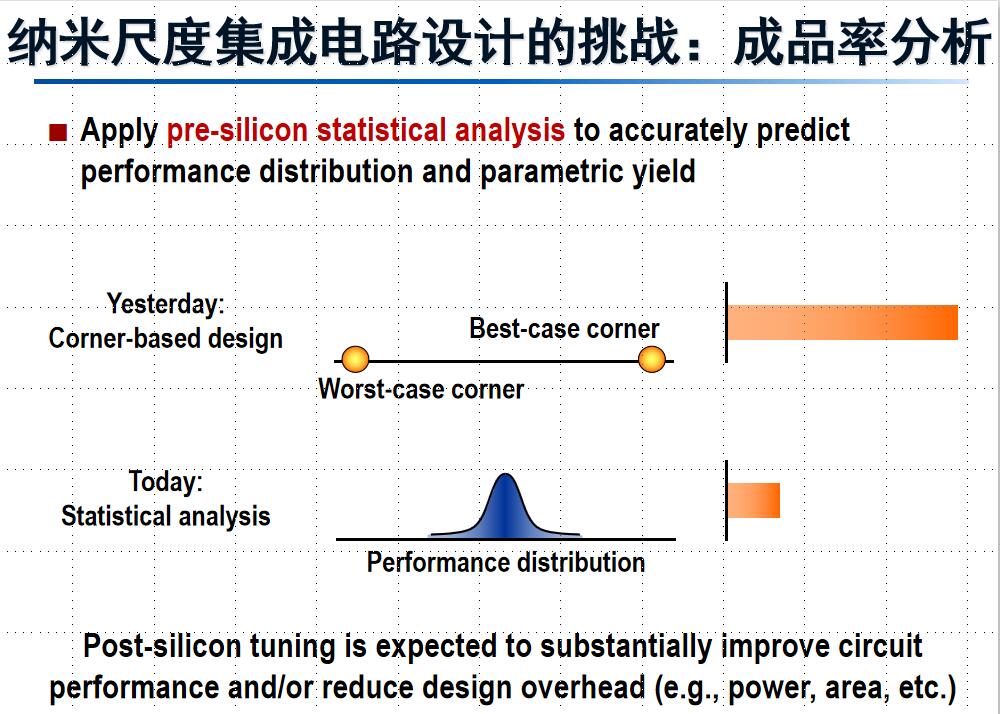

集成电路产业无疑是有史以来发展最为迅猛的产业之一,随着特征尺寸的持续不断缩小,集成电路的性能和集成度均以几何速度飞速增长。但集成电路制造工艺进入纳米时代后,严重的工艺参数盘查导致集成电路性能及成品率的迅速恶化,可制造性和成品率问题已成为纳米集成电路设计的致命性难题。

集成电路设计面临的挑战

集成电路是二十世纪五、六十年代发展起来的一种新型半导体器件。它是经过氧化、光刻、扩散、外延、蒸铝等半导体制造工艺,把构成具有一定功能的电路所需的晶体管、电阻、电容等元件及它们之间的连接导线全部集成在一小块硅片上,然后焊接封装在一个管壳内的电子器件。

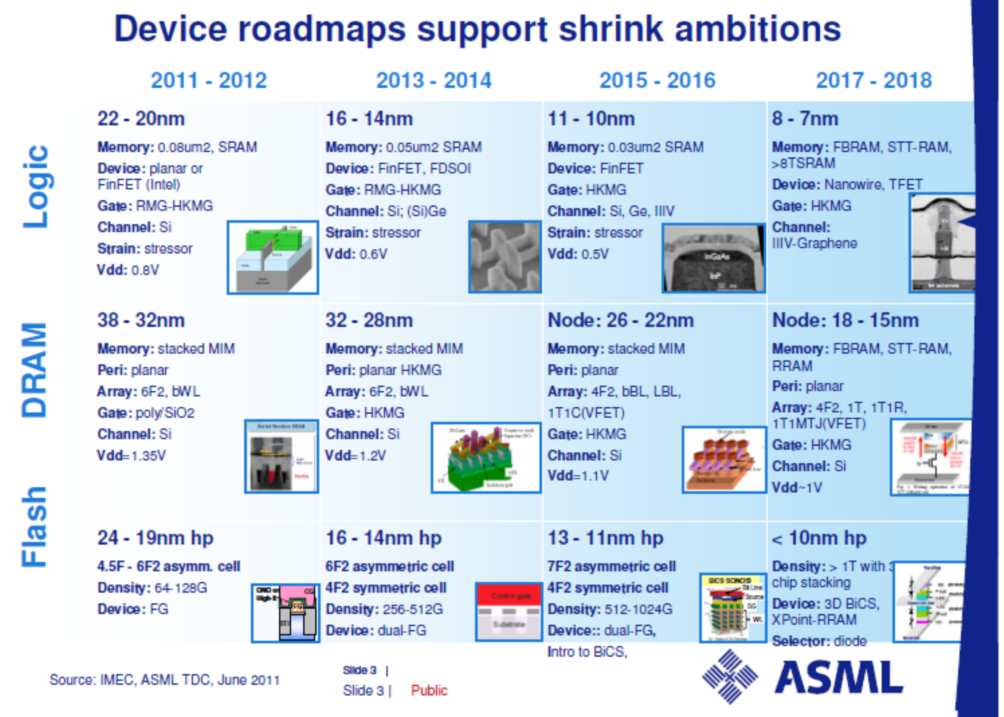

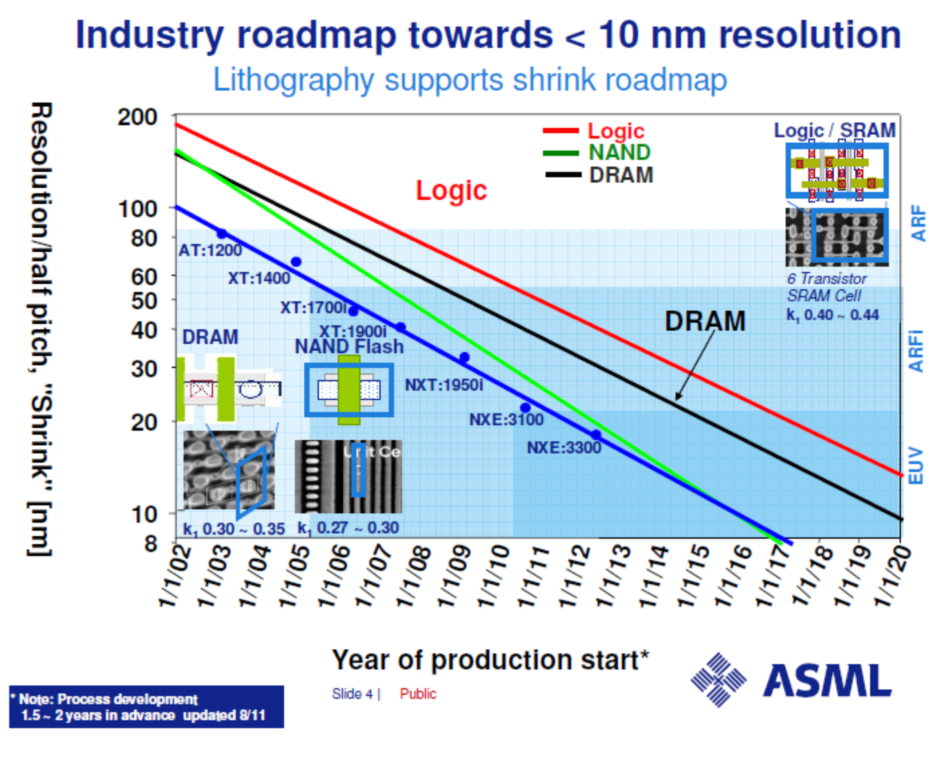

现有工艺已经可以做到7nm,在这样的尺度下,集成电路碰到一些非常困难的问题。首先,所有期间制造时都是用193nm,但是我们要做的尺寸已到7nm。还有就是现有的单重曝光已无法满足,遇见到了需要进行双重、三重、多重曝光的技术。

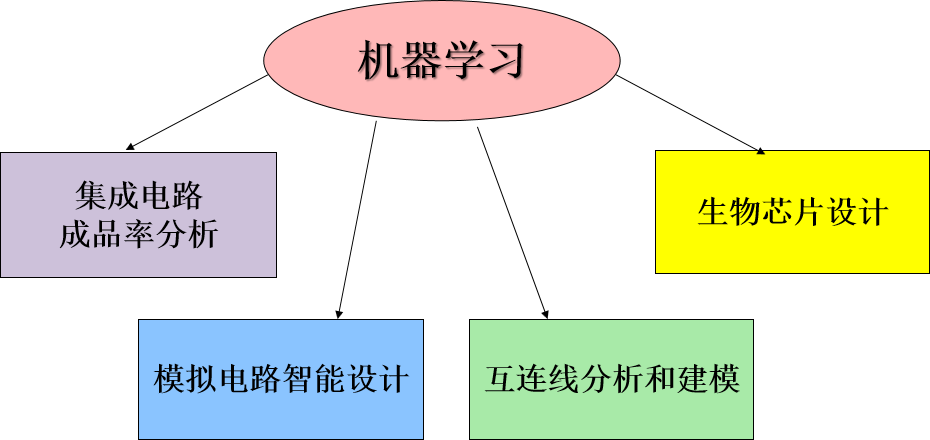

工艺的推进促使集成电路设计面临许多困难,我们做的器件、互连线跟板图设计完全不一样,这里面涉及到成平率、可靠性的问题,所以必须在设计阶段有新的发展,复旦大学曾博士及其团队采用基于及其学习的集成电路设计新方法,应用于集成电路成品率分析、模拟电路智能设计、互联线分析和建模、生物芯片设计等方面。

基于机器学习的集成电路统计分析方法

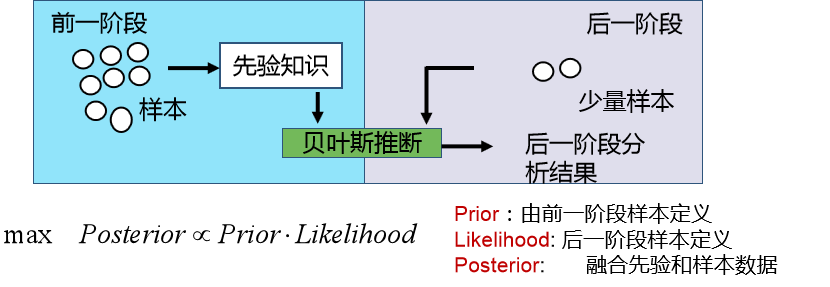

1、基于贝叶斯推断的成品率分析方法

- 在集成电路分析中,不可能收集到大量数据;

- 只能利用少量数据来获得尽可能高精度的结果;

√ 电路设计制造通常遵循设计流程

√ 同样的仿真和测量数据会在多个阶段进行测量

发展了一系列贝叶斯推断方法,提高分析效率达1个量级

√ 二元形式的贝叶斯推断方法[DAC’2014]

√ 多个相关的性能参数的贝叶斯推断方法[DAC’2015]

√ 多个先验的贝叶斯推断方法[DAC’2016]

√ 稀疏先验贝叶斯推断方法[DAC’2016]

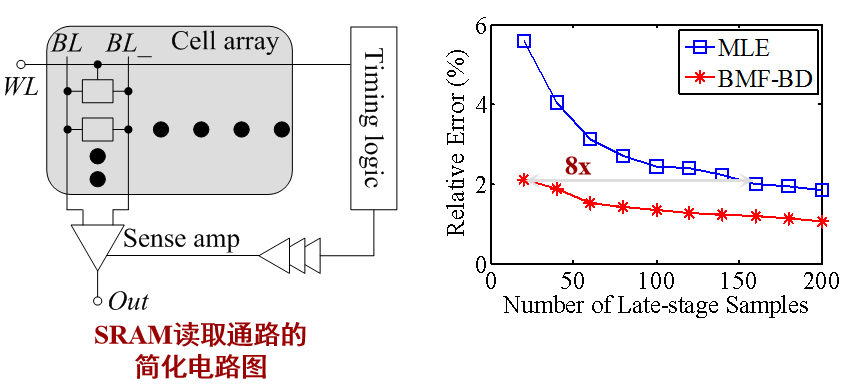

2、参数成品率测例: SRAM读取通路

SRAM读取通路采用65nm工艺设计

√ 前一阶段(前仿真)成品率: 89.88%

√ 后一阶段(后仿真)成品率: 90.66%

√ 本项目提出的方法相比传统的蒙特卡洛方法降低了8x的代价

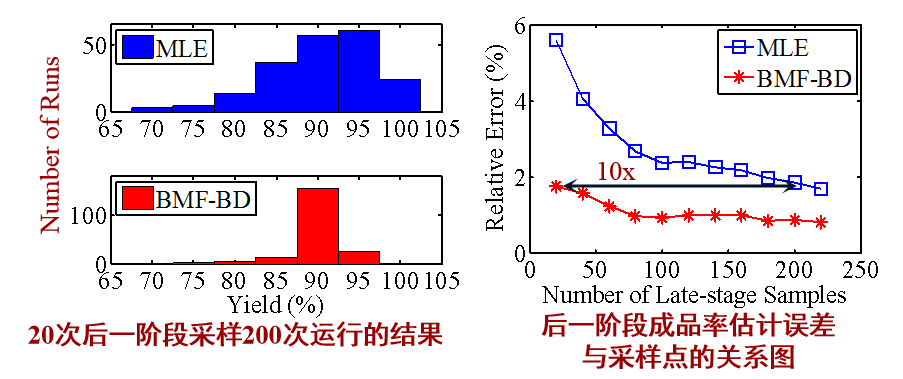

3、参数成品率测例:硅片实测结果

两次流片的硅片测试数据

√ 第一次流片成品率作为早期数据: 90.63%

√ 第二次流片成品率作为后期数据: 90.25%

√ 本项目提出的方法相比传统的蒙特卡洛方法降低了10x的代价

4、提出了基于压缩感知和贝叶斯推断的电路性能建模

利用贝叶斯推断,仅需测量40片芯片,与实测112片的电路性能精度相当,硅片测试成本降低了3倍,

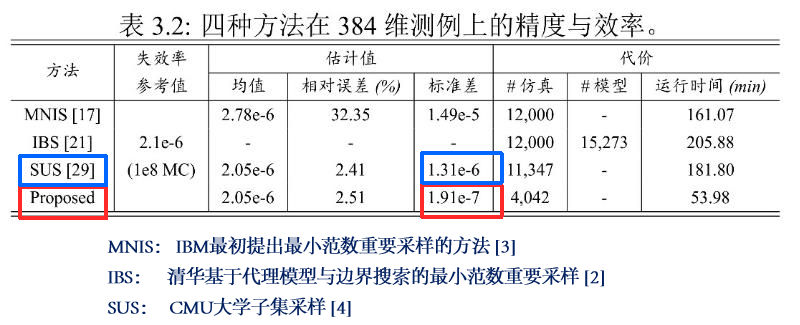

5、高维多失效区域SRAM失效率分析方法

√ 提出了基于高维、多失效区域重要采样的SRAM失效率分析方法MFRIS

√ 用多起始点优化算法解决高维工艺空间内、存在多失效区域时的 OSV 搜索问题,用自适应建模方法提高重要性采样的计算效率

√ 比美国CMU大学Xin Li教授的子集采样 SUS方法速度快3倍,估计值标准差减小1个量级

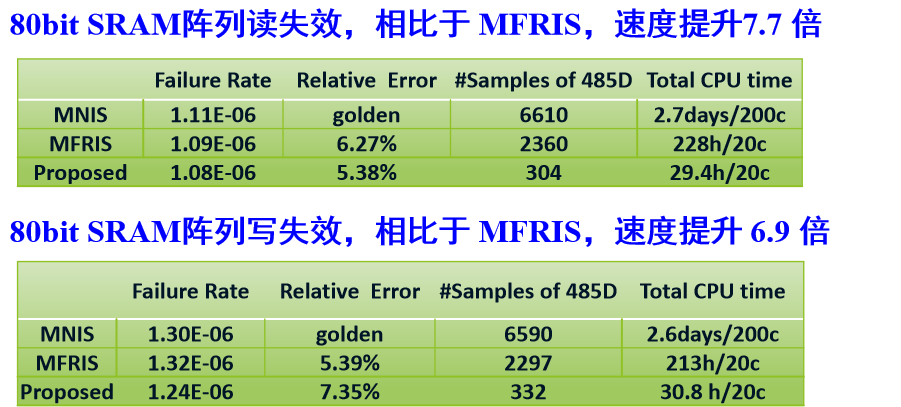

6、贝叶斯推断高维SRAM成品率分析

√ 提出了基于贝叶斯推断的高维SRAM 成品率分析方法,仅需要少量的高维电路仿真即可获取高维SRAM 电路极低失效率

√ 对485维80bit SRAM阵列,失效率分析速度比MFRIS方法(发表在2017年IEEE T-VLSI)提升6.9-7.7倍,被IEEE DAC’2018录用

模拟集成电路设计智能优化工具

1、模拟电路设计的挑战

- 从电路及设计(10-100晶体管)到系统级设计 (1000-10000晶体管)

- 非线性优化问题非常困难

√ 非凸问题

√ 局部最优和全局最优

- 高维非线性优化问题更加困难

- 纳米尺度集成电路设计

必须采用晶体管级仿真来保证精度

工艺偏差导致性能偏差和成品率损失

需要大量的PVT采样来进行成品率分析

2、模拟电路优化算法回顾

基于仿真的优化算法

- 模拟退火(TCAS-I, 2005),

- 进化算法(ISCAS, 2009),

- 粒子群算法(ICM, 2011), etc.

- 比利时鲁汶大学Georges Gielen教授工作

√ 全局优化的差分进化算法

√ 基于高斯过程的伴随模型来降低电路仿真次数

√ 二级差分运放的设计(TCAD,2011)、线性Rf放大器的设计 (TCAD, 2012), √ 毫米波集成电路设计 (TCAD, 2014).

- 基于模拟的优化方法基于电路仿真,精度最高,但计算复杂度较高

- 贝叶斯优化的模拟电路自动综合方法[IEEE TCAS-I 2018]

√ 设计效率比模拟退火、遗传、差分进化算法等提升3-5倍以上

√ 相比鲁汶大学G. Gielen教授提出的GASPAD优化方法,优化结果更优,仿真点数目减少到1/3到1/5

- 贝叶斯优化的成品率优化方法[IEEE TCAD 2018]

√ 效率相比鲁汶大学G. Gielen教授的ORDE算法提升5倍,优化结果相当

√ 对于SRAM电路相比清华大学提出方法效率提升100倍

- 多起始点优化和稀疏建模的模拟电路综合[IEEE TCAD 2017]

√ 相比模拟退火、差分进化、遗传、粒子群、半定规划,计算速度提升1.3~2100倍

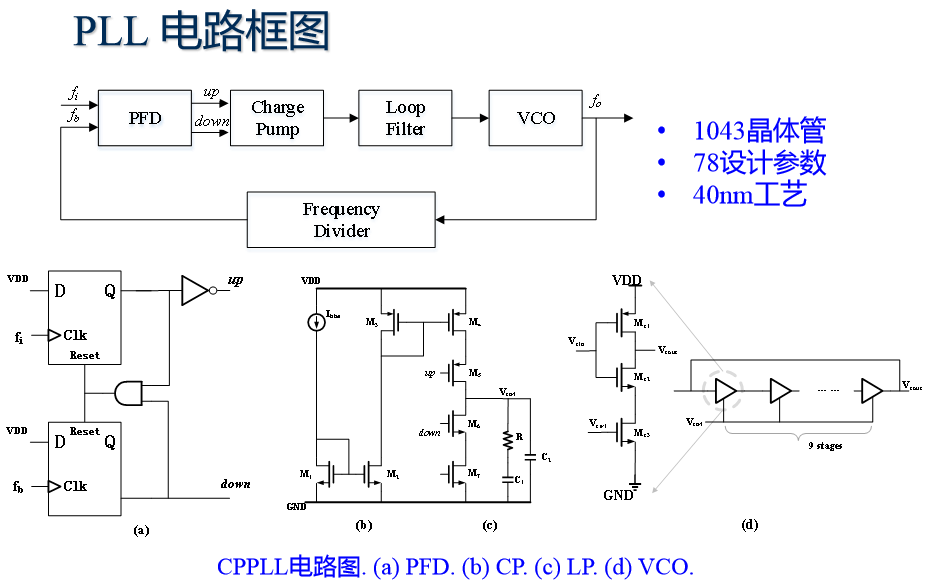

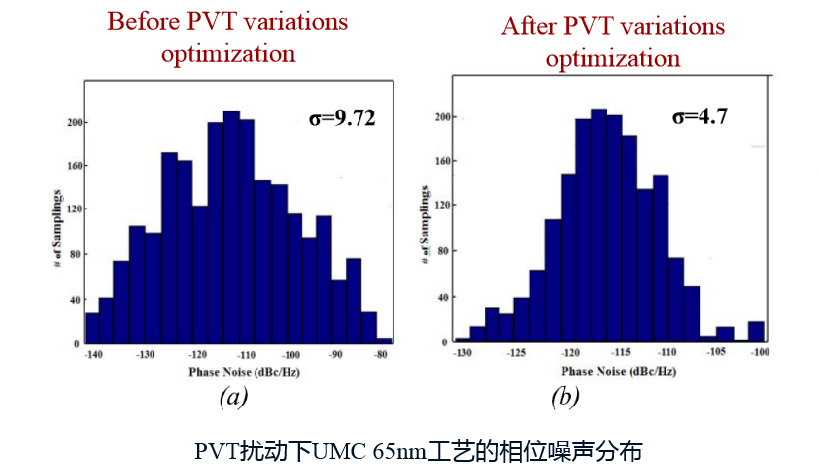

3、PLL设计

IBM 65nm和UMC 65nm工艺下的优化结果

工艺偏差下的结果:

经过优化后,相位噪声方差降低了 51.64%

运行时间:

UMC 65nm : 一轮优化耗费4.4小时

IBM 65nm: 两轮优化耗费17.5小时

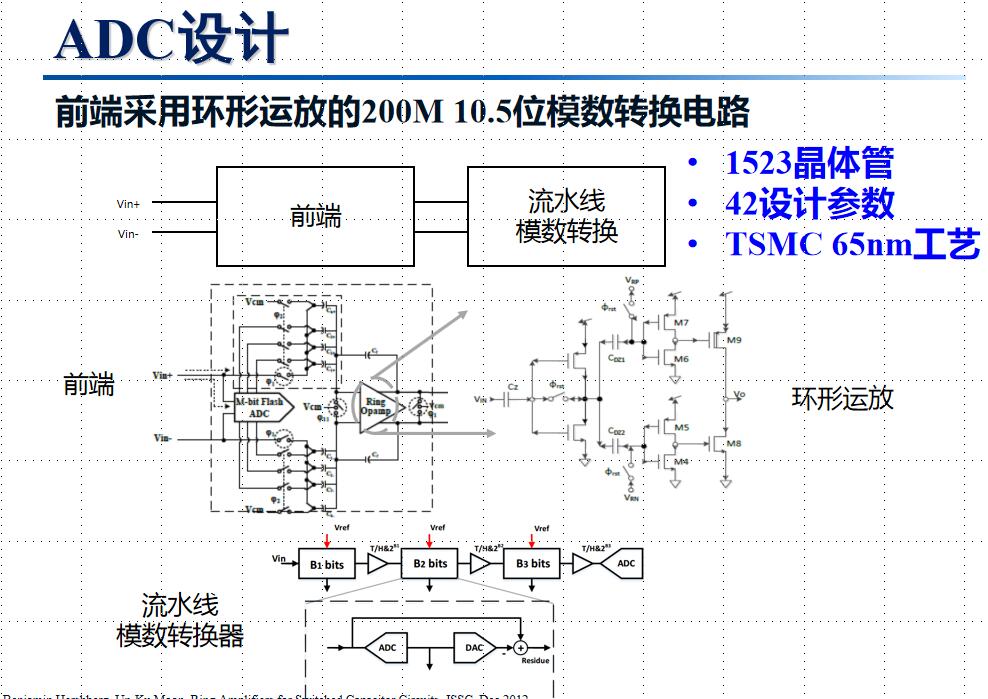

4、ADC设计

- 我们优化结果性能优于人工设计

- TSMC 65nm 工艺

- 1523 晶体管, 42 设计参数

- 采用行为级模型,10核下耗费21.6小时

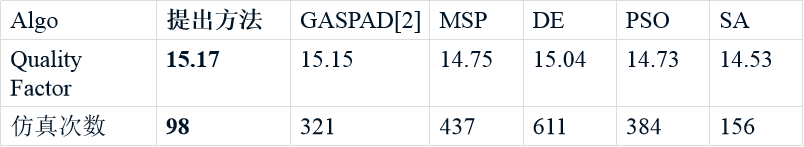

5、60GHz电感器件优化结果

60GHz电感:品质因数相当,平均仿真次数仅为比利时鲁汶大学George Gielen教授提出的GASPAD [1]方法提高1/3,效率提升3倍

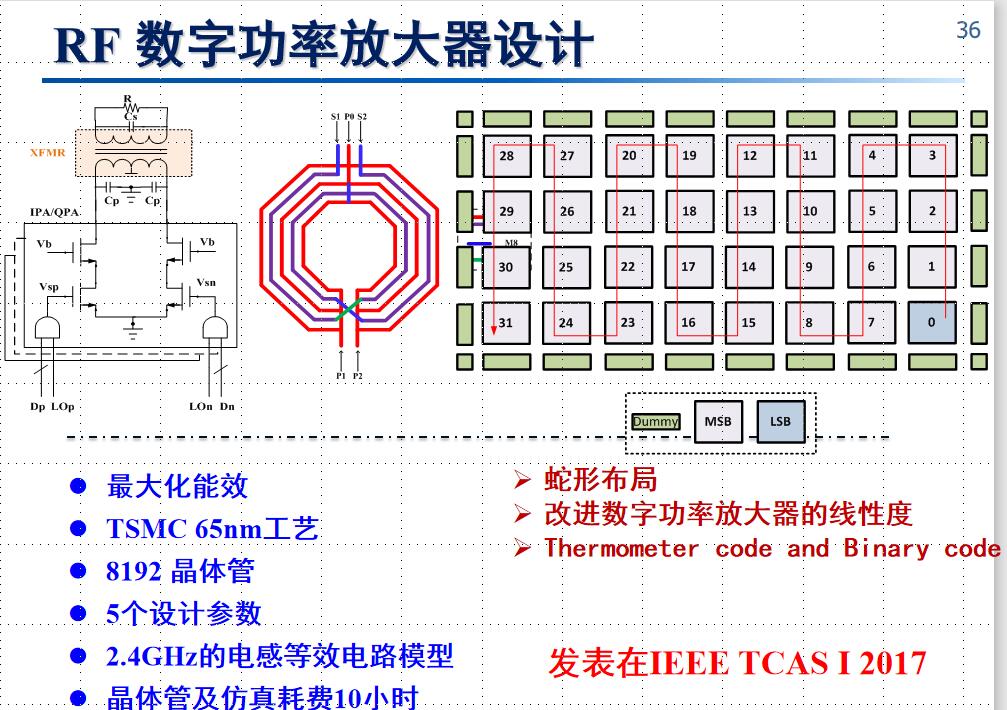

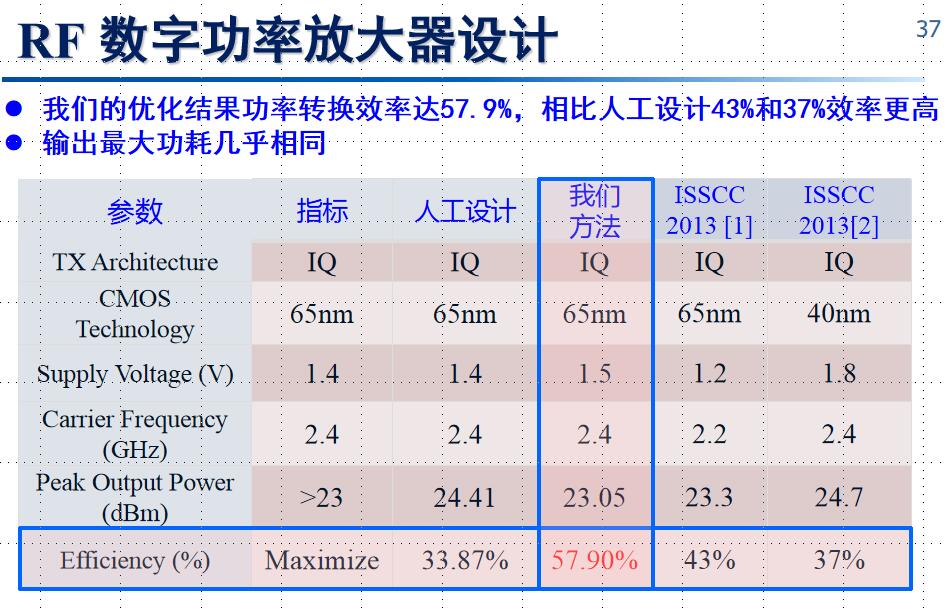

6、RF 数字功率放大器设计

运放电路成品率优化结果:

提出的贝叶斯优化方法,效率比比利时鲁汶大学George Gielen教授提出的ORDE [1]方法提高5倍, 成品率相当

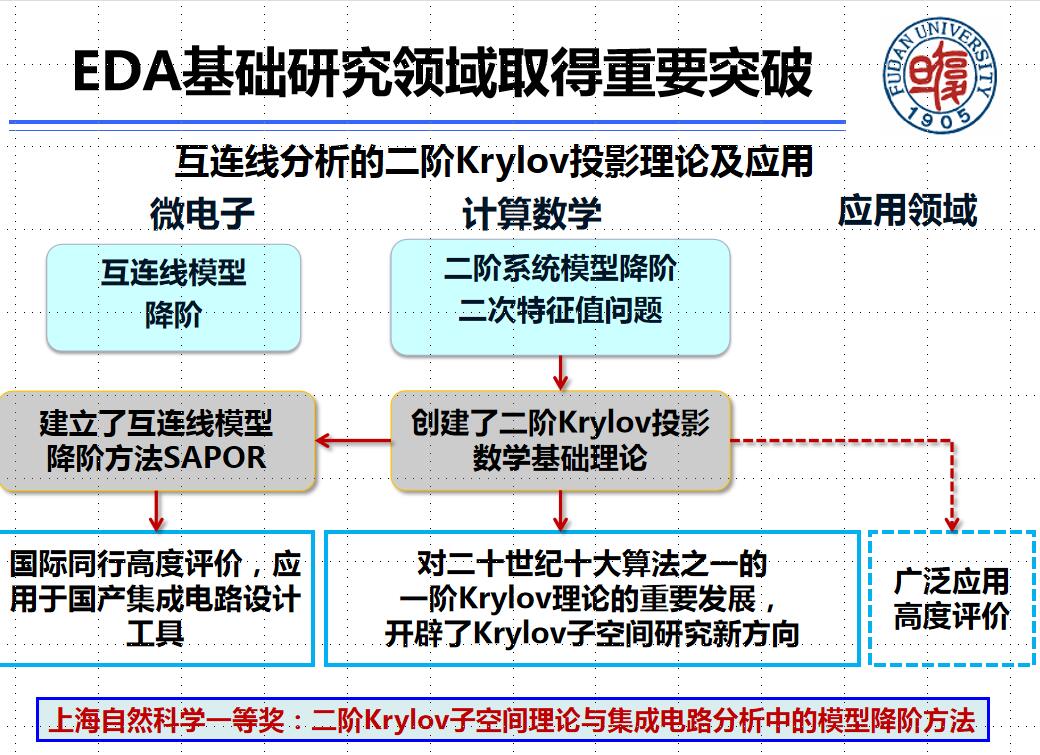

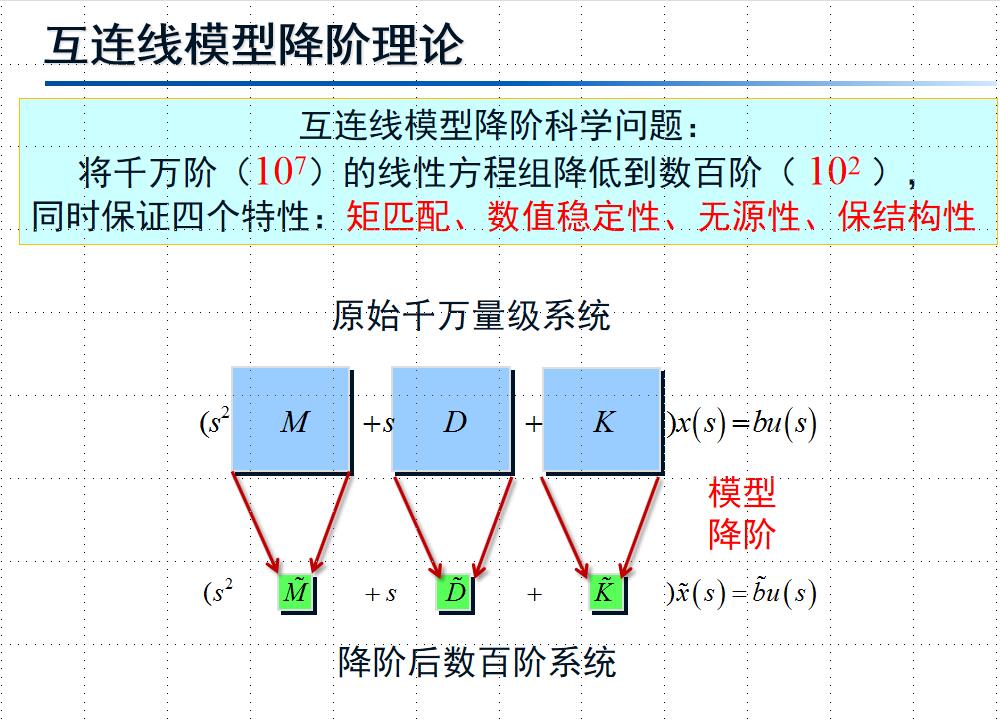

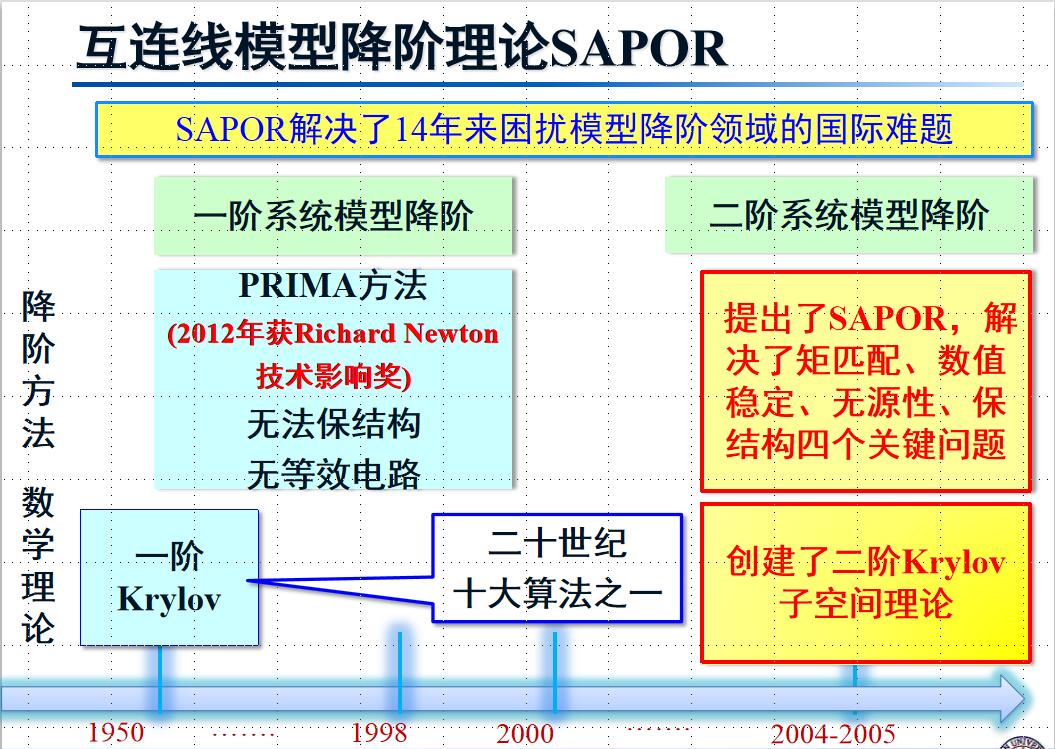

集成电路的互连线分析

集成电路:数亿晶体管+总长数公里互连线 ,信号在互连线上,传输时间决定芯片速度,为分析芯片速度,互连线建模为千万量级等效电路。

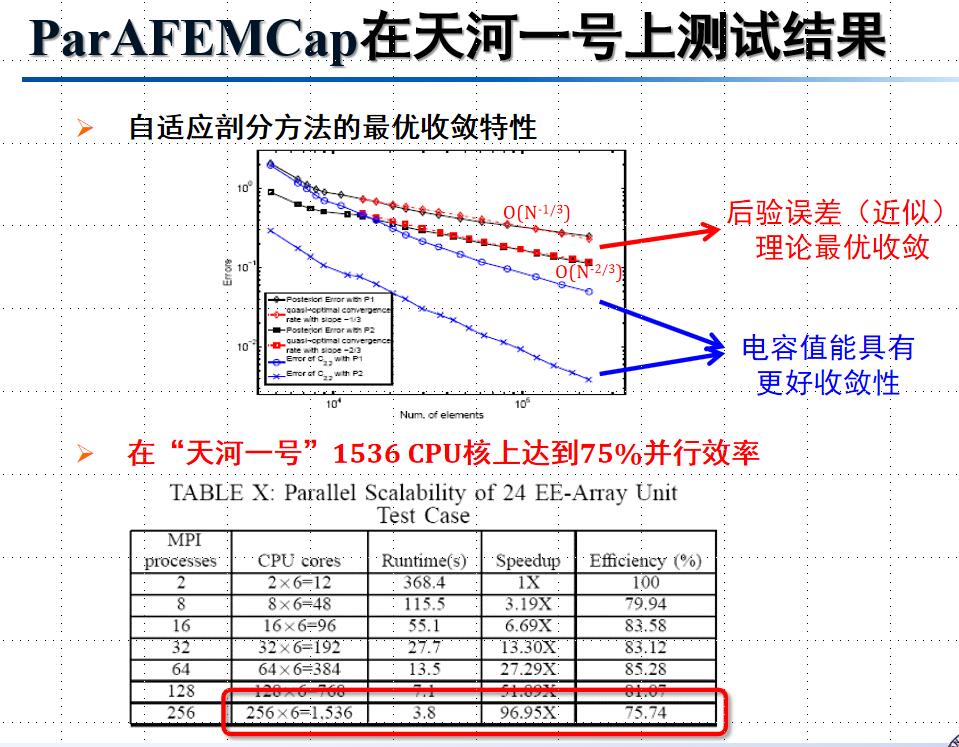

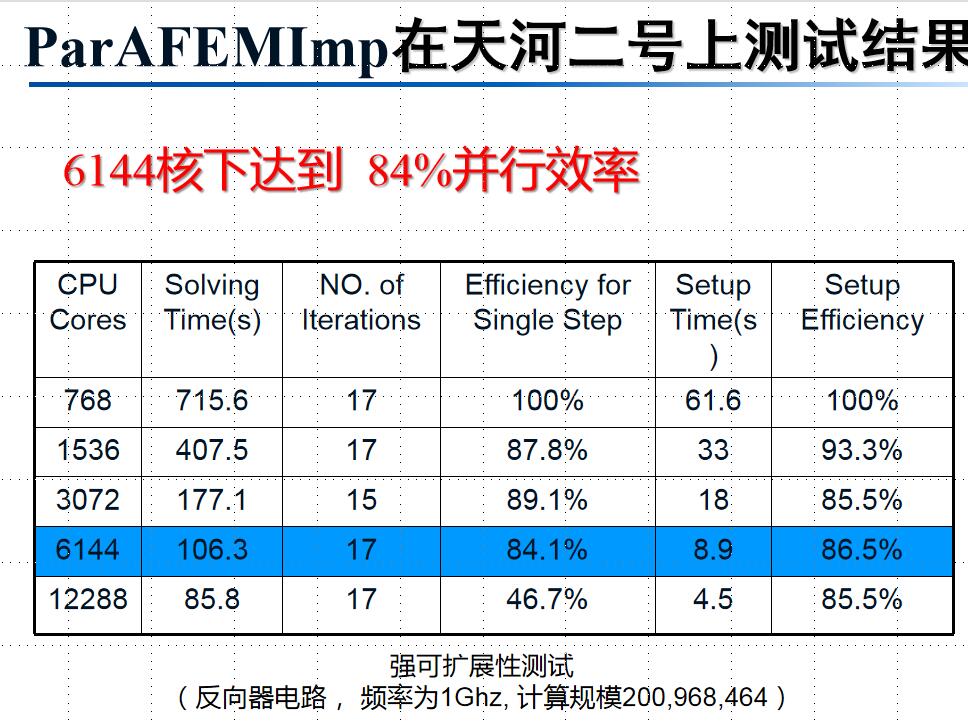

- 复旦大学与中科院计算数学所合作,将数亿自由度的并行自适应有限元方法应用于超大规模集成电路互连线参数提取

- 基于PHG平台的集成电路互连线寄生参数建模、仿真的高效并行数值方法

- 首次实现能在上千和上万CPU核上运行的参数提取工具

应用1:国际直线对撞机设计

斯坦福直线加速器中心将SOAR集成到Omega3P软件包,应用于研究国际直线对撞机中的高次模阻尼问题,并发现了新的物理现象。

应用2:“利用SOAR成功计算了320万阶9腔超导模型问题中的二次特征值问题。结果表明SOAR不仅速度上大大超过线性化Arnoldi方法,精度也更高。”

应用3:MEMS设计软件包MOR for ANSYS

德国Freiburg大学微系统技术研究所将 SOAR 集成到商业模型降阶软件包MOR for ANSYS中,其负责人在专著中指出该软件包实现了二阶系统的三种降阶方法,其中第三种方法就是利用SOAR进行保结构模型降阶

应用4:应用于频变电磁器件降阶

“本文提出的频变电磁器件降阶方法是基于对二阶动力系统降阶技术[14-17](即SAPOR)的拓展”

应用5:IEEE Fellow、美国UIUC 大学Cangellaris教授

应用SOAR研究频变电磁器件降阶

应用6:德国斯图加特大学P. Eberhard教授应用SOAR研究变形多体动力系统

应用7:加拿大麦吉尔大学R. Khazaka教授将SOAR应用于微波波导全波分析的模型降阶问题

应用8:汉堡工业大学H. Voss教授应用SOAR求解由正则化得到的大规模二次特征值问题

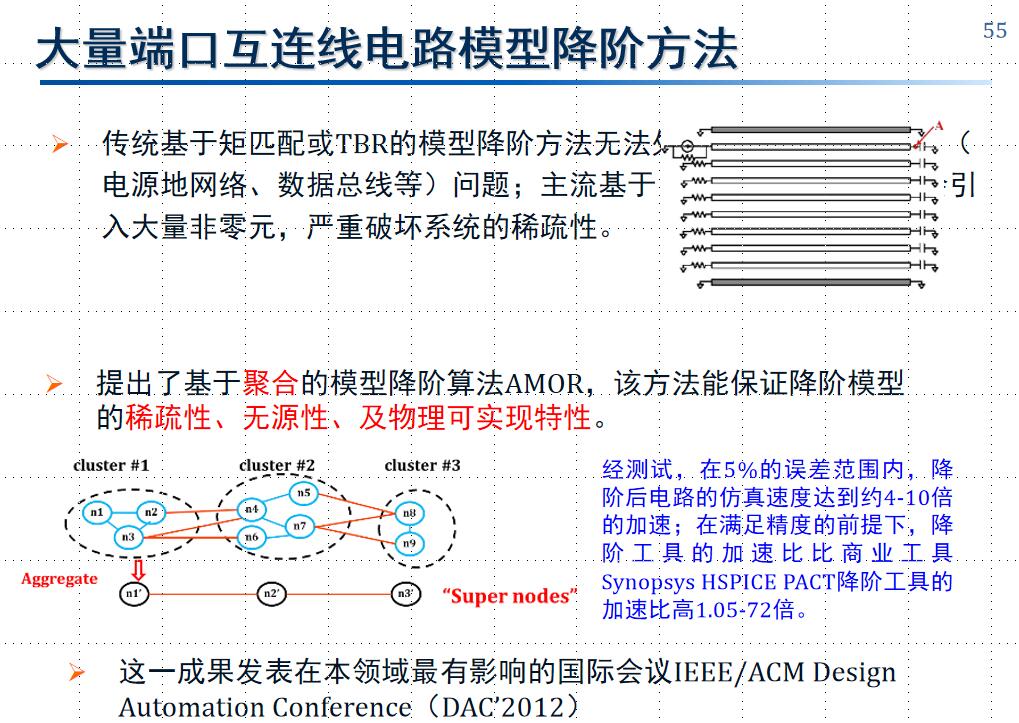

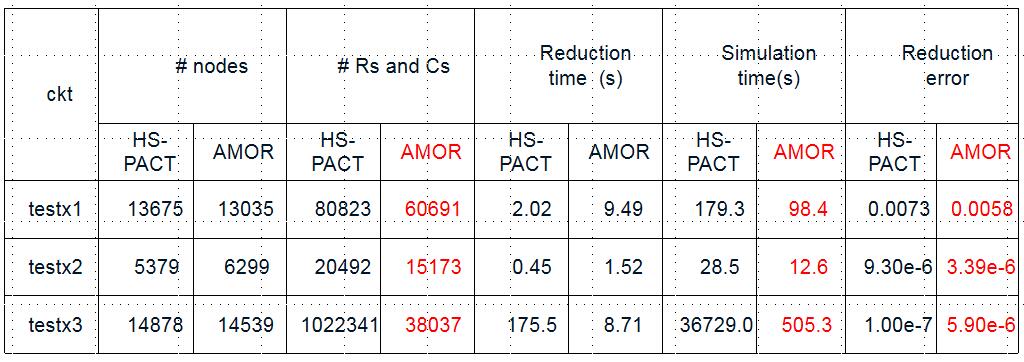

大量端口互连线电路模型降阶方法

在满足精度的前提下,降阶工具的加速比比商业工具Synopsys HSPICE PACT降阶工具的加速比高1.05-72倍

AMOR比Cadence商业工具快3.4-7.28倍

生物芯片设计

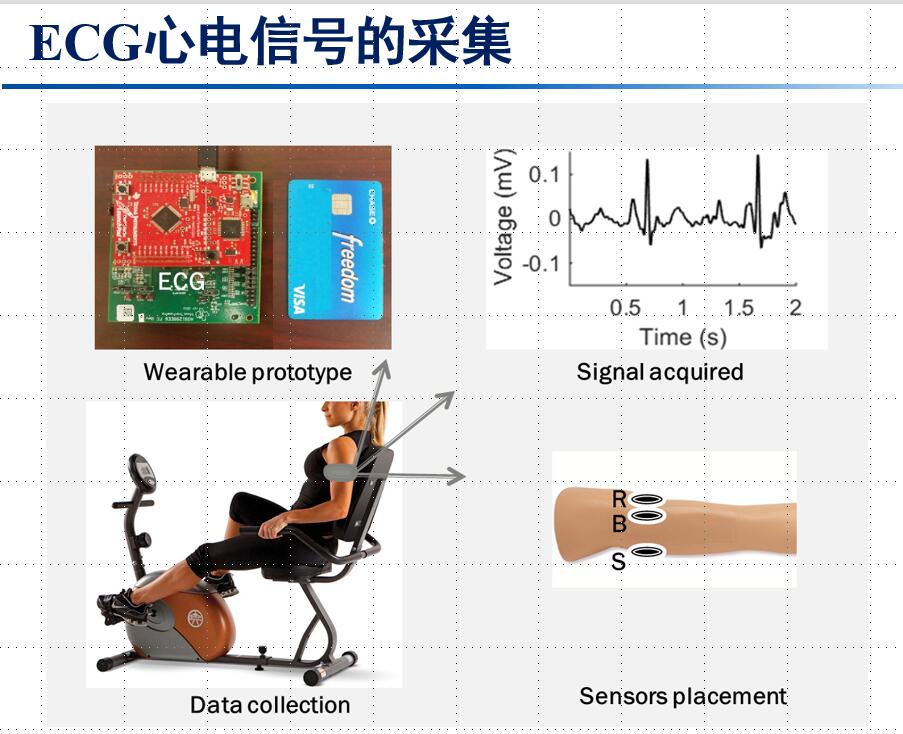

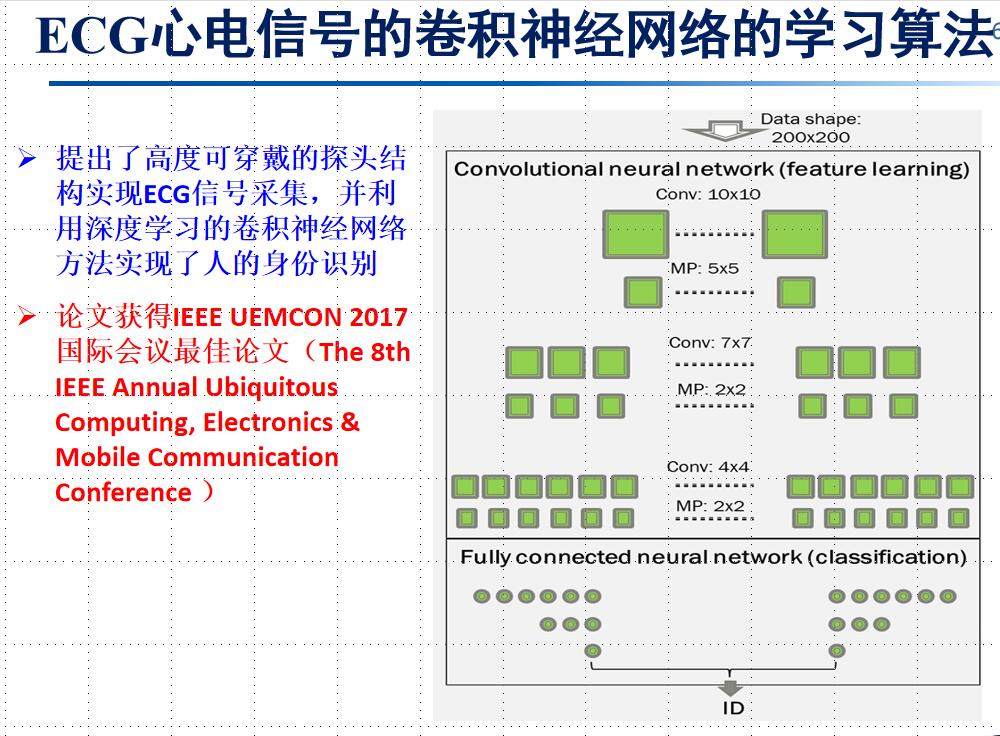

智能可穿戴设备

采用ECG信号实现人的身份识别

√ 普适性

√ 容易测量

√ 唯一性

√ 永久性

集成电路设计技术的进步不断给工艺技术的发展提出更高要求,同时工艺技术的更新换代又称为设计技术不断进步的动力。人工智能技术将在集成电路设计方法上产生革命性变化,为集成电路设计方法和新工具带来新的产业机遇。元王也将不断进步提高CAE仿真技术,深耕CAE软件研发,适应时代的发展,为客户创造价值,为国内CAE仿真行业发展做出贡献。